## **NEC 304**

# STLD

Lecture 30

Random Access Memory (RAM)

Rajeev Pandey Department Of ECE rajeevvce2007@gmail.com

#### **Overview**

- <sup>o</sup> Memory is a collection of storage cells with associated input and output circuitry

- Possible to read and write cells

- <sup>o</sup> Random access memory (RAM) contains words of information

- ° Data accessed using a sequence of signals

- Leads to timing waveforms

- ° Decoders are an important part of memories

- Selects specific data in the RAM

- Static RAM loses values when circuit power is removed.

#### **Preliminaries**

#### ° RAMs contain a collection of data bytes

- A collection of bytes is called a word

- A sixteen bit word contains two bytes

- Capacity of RAM device is usually described in bytes (e.g. 16 MB)

- <sup>°</sup> Write operations write data to specific words

- ° Read operations read data from specific words

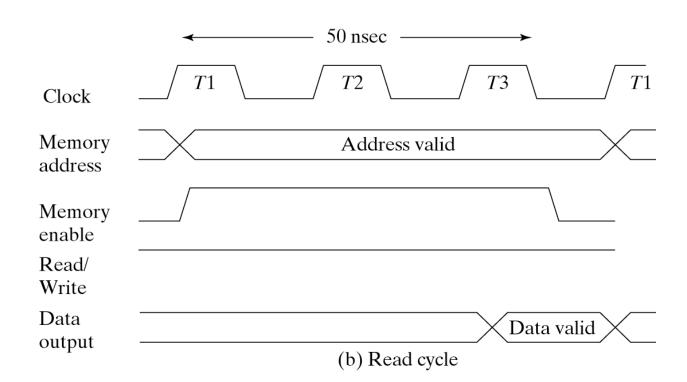

- ° Note: new notation for OR gate

Fig. 7-1 Conventional and Array Logic Diagrams for OR Gate

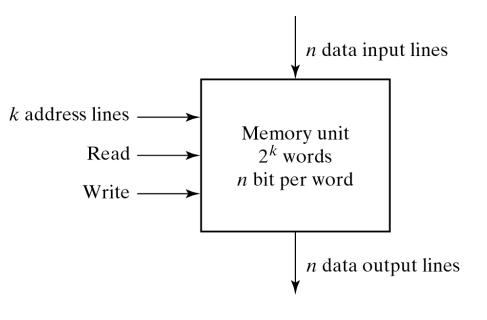

#### **RAM Interface Signals**

- <sup>°</sup> Data input and output lines carry data

- <sup>°</sup> Memory contains 2<sup>k</sup> words

- k address lines select one word out of 2<sup>k</sup>

- <sup>°</sup> Read asserted when data to be transferred to output

- <sup>o</sup> Write asserted when data input to be stored

Fig. 7-2 Block Diagram of a Memory Unit

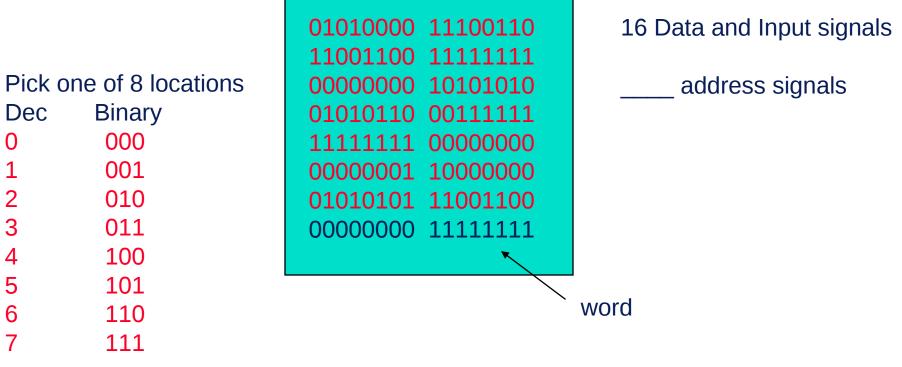

#### **Random Access Memory Fundamentals**

#### ° Lets consider a simple RAM chip

- 8 words of 2 bytes each (each word is 16 bits)

- How many address bits do we need?

Each bit stored in a binary cell

## **RAM Size**

| ° If memory has 2 <sup>k</sup> words, k<br>address bits are needed | Men       |

|--------------------------------------------------------------------|-----------|

| audiess bits are needed                                            | Binary    |

| ° 2³ words, 3 address<br>bits                                      | 000000000 |

|                                                                    | 000000000 |

| ° Address locations are<br>labelled 0 to 2 <sup>k</sup> -1         | 000000001 |

| ° Common subscripts:                                               |           |

| ° Kilo – 2 <sup>10</sup>                                           | 111111110 |

| 0.0.0.000                                                          | 111111111 |

| ° Mega – 2 <sup>20</sup>                                           | 111111111 |

| ° Giga - 2 <sup>30</sup>                                           |           |

|                                                                    |           |

| ress    |                        |

|---------|------------------------|

| decimal | Memory contest         |

| 0       | 1011010101011101       |

| 1       | 1010101110001001       |

| 2       | 0000110101000110       |

| •       | :                      |

| •       | :                      |

| 1021    | 1001110100010100       |

| 1022    | 0000110100011110       |

| 1023    | 1101111000100101       |

|         | decimal<br>0<br>1<br>2 |

Fig. 7-3 Content of a  $1024 \times 16$  Memory

#### **Write Operation**

- 1. Apply binary address of word to address lines

- 2. Apply data bits to data input lines

- **3. Activate write input**

Data output lines unused

Read input signal should be inactive

Delay associated with write

Fig. 7-2 Block Diagram of a Memory Unit

#### **Read Operation**

- 1. Apply binary address of word to address lines

- 2. Activate read input

Data input lines unused Write input signal should be inactive

Delay associated with read

Memory enable used to allow read and writes

Fig. 7-2 Block Diagram of a Memory Unit

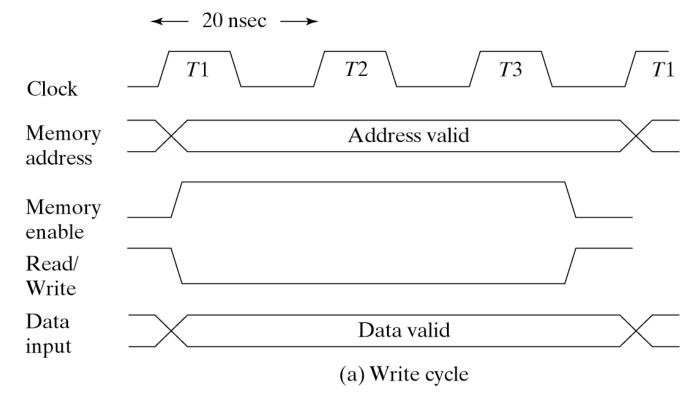

### **Memory Timing – write operation**

- Memory does not use a clock

- Control signals may be generated on clock edges

- ° Cycle time time needed to write to memory

- If cycle time is 50 ns, 3 clock edges required (T1, T2, T3)

#### **Timing Waveforms – read operation**

- Access time indicates time to read

- Address indicates location

- Data valid on Data Output following access time

Fig. 7-4 Memory Cycle Timing Waveforms

Multiple clock signals needed for data read in this example \* Note ordering of signals (address, mem enable)

#### **Comments about Memory Access and Timing**

- Most computers have a central processing unit (CPU)

- Processor generates control signals, address, and data

- Values stored and then read from RAM

- The timing of the system is very important.

- Processor provides data for the cycle time on writes

- Processor waits for the access time for reads

#### **Types of Random Access Memories**

#### <sup>o</sup> Static random access memory (SRAM)

- Operates like a collection of latches

- Once value is written, it is guaranteed to remain in the memory as long as power is applied

- Generally expensive

- Used inside processors (like the Pentium)

#### <sup>°</sup> Dynamic random access memory (DRAM)

- Generally, simpler internal design than SRAM

- Requires data to be rewritten (refreshed), otherwise data is lost

- Often hold larger amount of data than SRAM

- Longer access times than SRAM

- Used as main memory in computer systems

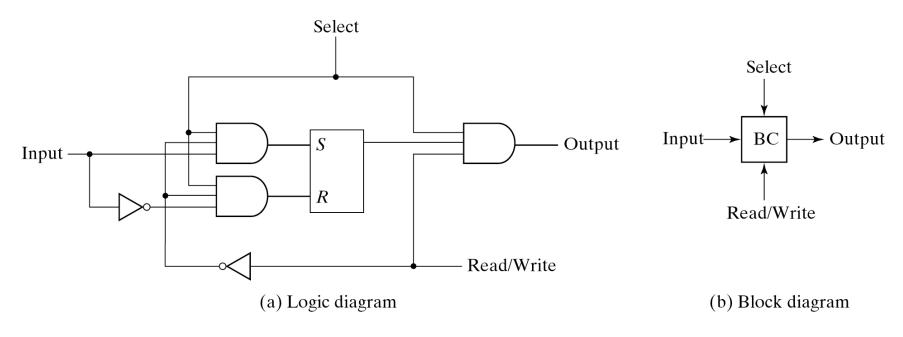

# Inside the RAM Device

Output uu

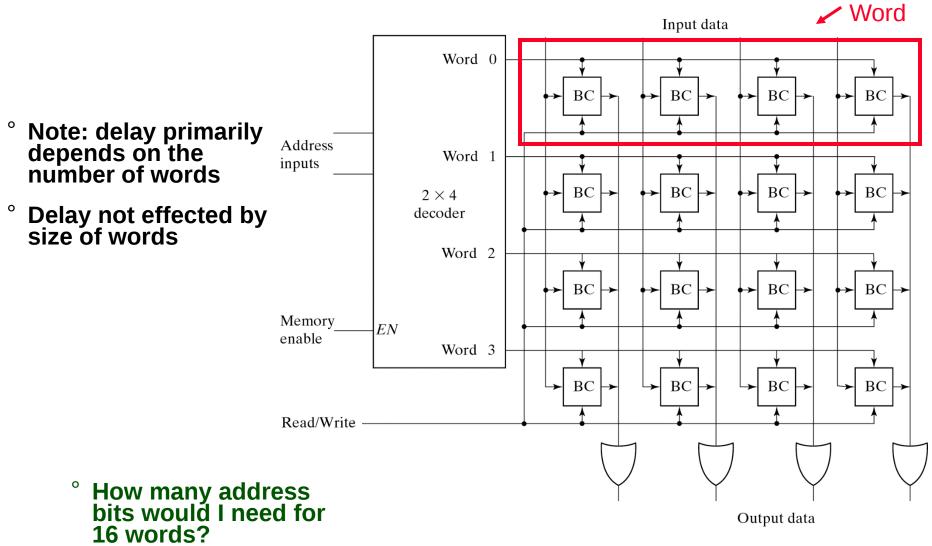

Fig. 7-6 Diagram of a 4  $\times$  4 RAM

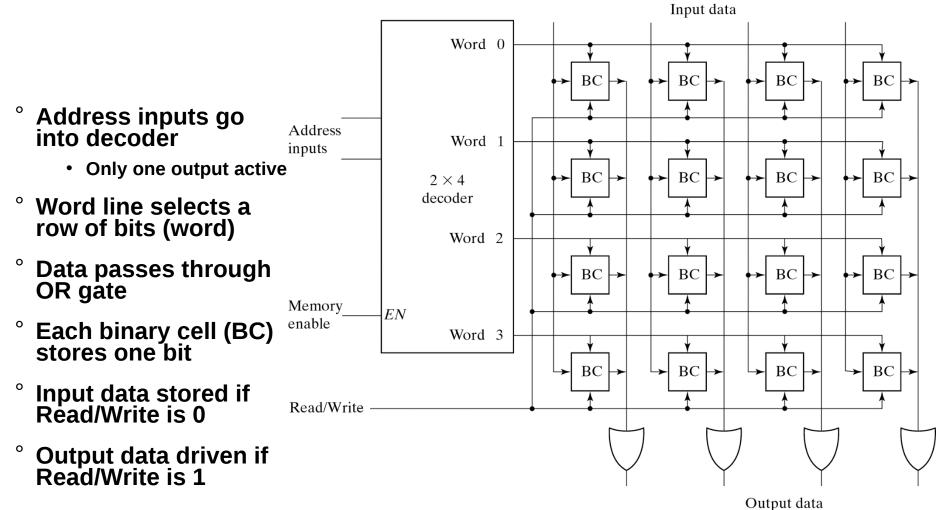

**Inside the SRAM Device**

- ° Basis of each SRAM cell is an S-R latch

- $^{\circ}$  Note that data goes to both S and R

- ° Select enables operation

- ° Read/write enables read or write, but not both

Fig. 7-5 Memory Cell

#### **Inside the SRAM Device**

Fig. 7-6 Diagram of a  $4 \times 4$  RAM

#### Summary

- <sup>°</sup> Memories provide storage for computers

- ° Memories are organized in words

- Selected by addresses

- ° SRAMs store data in latches

- Accessed by surrounding circuitry

- ° RAM waveforms indicate the control signals needed for access

- ° Words in SRAMs are accessed with decoders

- Only one word selected at a time